Solved 68hc11 Instruction Set Based Question Please Help Chegg

Solved 68hc11 Instruction Set Based Question Please Help Chegg Not the question you’re looking for? post any question and get expert help quickly. Branch instructions: (except for brclr and brset) do not affect the condition code flags. arithmetic shifts: arithmetic shift left is the same as a logical shift left; arithmetic shift right preserves the sign bit and shifts the least significant bit into the c flag.

Solved 68hc11 Instruction Set Based Question Please Help Chegg 68hc11 instruction set. modified and corrected from tom dickens. please notify me of any errors!. The instruction contains the address of the memory location where the data or operand is stored. direct addressing always deals with data or operands stored in memory. there are two options for direct addressing: short and extended examples: address code mnemonic instruction actions. What do accumulators a and b, index register ix, and ccr bits n, z, v, and c contain after each instruction?. ** 12 cycles are used beginning with the opcode fetch. a wait state is entered which remains in effect for an integer number of mpu e clock cycles (n) until an interrupt is recognized. finally, two additional cycles are used to fetch the appropraite interrupt vector (14 n total).

68hc11 Instruction Set Pdf What do accumulators a and b, index register ix, and ccr bits n, z, v, and c contain after each instruction?. ** 12 cycles are used beginning with the opcode fetch. a wait state is entered which remains in effect for an integer number of mpu e clock cycles (n) until an interrupt is recognized. finally, two additional cycles are used to fetch the appropraite interrupt vector (14 n total). The 68hc11 operates in the expanded mode inside the evbplus2 because external memory needs to be accessed. this would mean that ports b and c are not available for i o. but we have already used port b for output (to drive the 8 leds) in our experiments! this dilemma has been solved by a special ic: the port replacement unit (68hc24). Question: for microcontroller 68hc11, utilize instruction delays to generate the one second delay. your code should have two nested loops. please use the 65456 to control the limit of one of the loops. document how you obtained exactly the 1 second delay with an 8mhz crystal. Add instruction — corrected table head from adca to adda 496 and instruction — corrected table head from adca to anda 498 asl instruction — corrected table heads asla (imm) to asla. Fortunately, the 68hc11 branch instructions will perform this interpretation properly, provided the correct instruction is used for the type of data the programmer has in mind. here is a list of some of the conditional branching instructions supported by the 68hc11:.

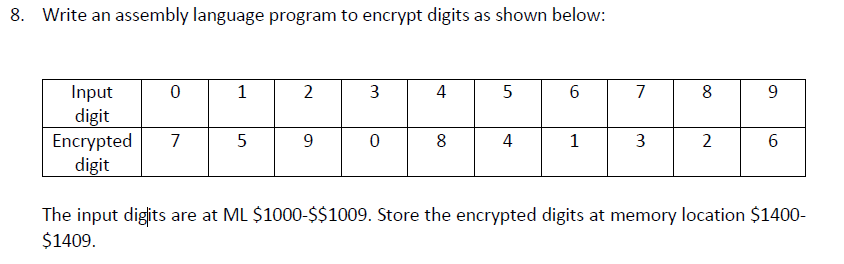

Solved Using 68hc11 Instruction Set Write And Assembly Chegg The 68hc11 operates in the expanded mode inside the evbplus2 because external memory needs to be accessed. this would mean that ports b and c are not available for i o. but we have already used port b for output (to drive the 8 leds) in our experiments! this dilemma has been solved by a special ic: the port replacement unit (68hc24). Question: for microcontroller 68hc11, utilize instruction delays to generate the one second delay. your code should have two nested loops. please use the 65456 to control the limit of one of the loops. document how you obtained exactly the 1 second delay with an 8mhz crystal. Add instruction — corrected table head from adca to adda 496 and instruction — corrected table head from adca to anda 498 asl instruction — corrected table heads asla (imm) to asla. Fortunately, the 68hc11 branch instructions will perform this interpretation properly, provided the correct instruction is used for the type of data the programmer has in mind. here is a list of some of the conditional branching instructions supported by the 68hc11:.

Comments are closed.