Solved Given A Timer Configuration As Follows Clock Source Chegg

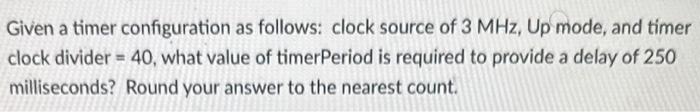

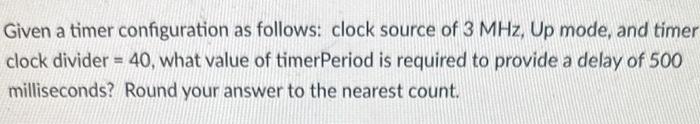

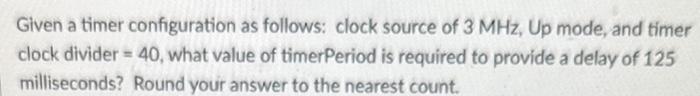

Solved Given A Timer Configuration As Follows Clock Source Chegg Question: given a timer configuration as follows: clock source of 3mhz, up mode, and timer clock divider =40, what value of timerperiod is required to provide a delay of 500 milliseconds? round your answer to the nearest count. Timer 0 counts up with the passing of each clock, which is provided by the crystal oscillator. as the timer counts up, it goes through the states of fff3, fff4, fff5, fff6, fff7, fff8, fff9, fffa, fffb, and so on.

Solved Given A Timer Configuration As Follows Clock Source Chegg A timer is a device used to measure and keep track of elapsed time. it is commonly used in various a. (a) for a specific application timera2 is configured as shown below. what is the timer clock source, the timer mode, the clock divider and the exact time between interrupts? is the timer enabled? if not, correct the code. Ask any question and get an answer from our subject experts in as little as 2 hours. It boots up with hsi as the clock source. my guess is you didn't change it from that, or your call to change the source to hse failed. if you feel a post has answered your question, please click "accept as solution".

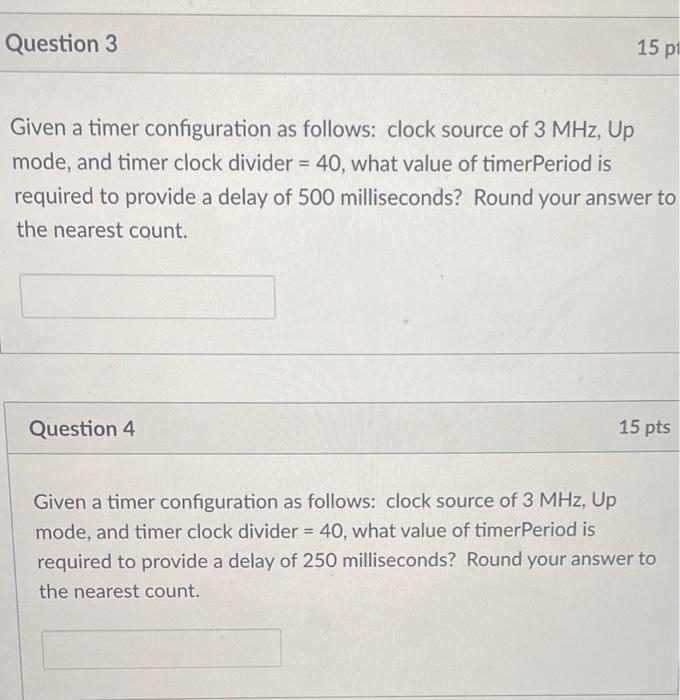

Solved Given A Timer Configuration As Follows Clock Source Chegg Ask any question and get an answer from our subject experts in as little as 2 hours. It boots up with hsi as the clock source. my guess is you didn't change it from that, or your call to change the source to hse failed. if you feel a post has answered your question, please click "accept as solution". Incorrect question 3 0 15 pts given a timer configuration as follows: clock source of 3 mhz, up mode, and timer clock divider = 40, what value of timerperiod is required to provide a delay of 500 milliseconds?. The timer clock source is smclk, which is typically set to 1 mhz. the timer clock divider is 32. finally, since the timer mode is continuous, we need to know the number of timer counts between each taifg flag. In pwm mode, the timer module is clocked from an internal clock source and produces a digital waveform on the output channel pin called the pwm signal. by using output compare registers (ocr), the incrementing timer’s register value is constantly compared against this ocr register. A. if there is no clock skew, what is the maximum operating frequency of this circuit? solution: tc ≥ tpcq tpd tsetup longest path: tc ≥ tpcq 3*tpd tsetup tc ≥ 70 3*100 60 = 430 ps max frequency = 1 tc = 2.33 ghz b. how much clock skew can the circuit tolerate before it might experience a hold time violation? solution:.

Solved Given A Timer Configuration As Follows Clock Source Chegg Incorrect question 3 0 15 pts given a timer configuration as follows: clock source of 3 mhz, up mode, and timer clock divider = 40, what value of timerperiod is required to provide a delay of 500 milliseconds?. The timer clock source is smclk, which is typically set to 1 mhz. the timer clock divider is 32. finally, since the timer mode is continuous, we need to know the number of timer counts between each taifg flag. In pwm mode, the timer module is clocked from an internal clock source and produces a digital waveform on the output channel pin called the pwm signal. by using output compare registers (ocr), the incrementing timer’s register value is constantly compared against this ocr register. A. if there is no clock skew, what is the maximum operating frequency of this circuit? solution: tc ≥ tpcq tpd tsetup longest path: tc ≥ tpcq 3*tpd tsetup tc ≥ 70 3*100 60 = 430 ps max frequency = 1 tc = 2.33 ghz b. how much clock skew can the circuit tolerate before it might experience a hold time violation? solution:.

Comments are closed.