Sn74hc595 How To Cascade Two Sn74hc595 Logic Forum Logic Ti E2e Support Forums

Sn74hc595 When Cascade Two Part Sn74hc595 The Secord Part Has Some Randomly Error In Some Bit Qh' output is a serial output which is necessary for cascading these devices. this output needs to be connected to the following hc595 device ser pin to allow the serial data to flow through each additional device. thanks for the reply. Hi, its possible to cascade 74hc595? i need to control 7 display to show frequency generated with ad9833. its possible to do with arduino? which considerations should i have? and with the code, its there any "easy way" to not o crazy with them? thanks.

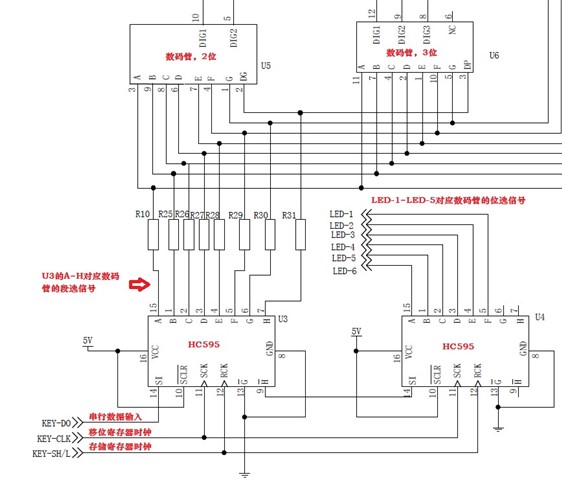

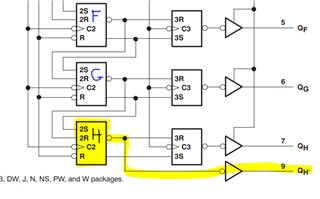

Sn74hc595 When Cascade Two Part Sn74hc595 The Secord Part Has Some Randomly Error In Some Bit The shift register has a direct overriding clear (srclr) input, serial (ser) input, and serial outputs for cascading. when the output enable ( oe ) input is high, the outputs are in the high impedance state. Further 595s can be cascaded with the 2 clock leads connecting to the appropriate pine on each chip and the q7' cascading to the ds pin of the nect chip in the chain. it is not normally necessary to use the reset pin on the chips. My customer use two part sn74hc595 to drive 16 bit output, but the second part output always has some error. it seems randomly. the schematic is as below. the customer has do some probe, please refer to the below picture. In your case, two 74hc595 and two 74hc165 (or 74hc597) in series, followed by your controller's shift register (number five). the controller has the miso mosi inputs outputs and controls clocking of the whole ring.

Sn74hc595 When Cascade Two Part Sn74hc595 The Secord Part Has Some Randomly Error In Some Bit My customer use two part sn74hc595 to drive 16 bit output, but the second part output always has some error. it seems randomly. the schematic is as below. the customer has do some probe, please refer to the below picture. In your case, two 74hc595 and two 74hc165 (or 74hc597) in series, followed by your controller's shift register (number five). the controller has the miso mosi inputs outputs and controls clocking of the whole ring. Cascading multiple sn74hc595 shift registers. you can connect multiple sn74hc595s together to control 16, 24, or more outputs. data shifts from the first sn74hc595 to the second one, allowing more outputs. Can you tell us a recommended gnd and vdd pattern on sn74hc595nsr and sn74hc595dr. Separate clocks are provided for both the shift and storage register. the shift register has a direct overriding clear (srclr) input, serial (ser) input, and serial outputs for cascading. when the output enable (oe) input is high, the outputs are in the high impedance state. In this project, we are going to cascade 2 shift registers together using the 74hc595 shift register. this means that we pretty connect them together, so that instead of controlling 8 outputs, the cascaded shift registers can now control 16 outputs.

Comments are closed.